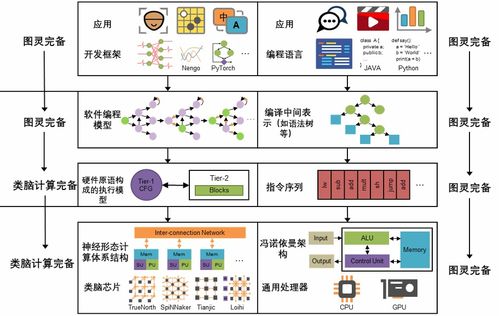

隨著人工智能技術的飛速發(fā)展,清華大學張悠慧教授提出的"類腦計算完備性"理念,正為計算機體系結構帶來革命性的思考。在傳統(tǒng)圖靈完備性已無法完全滿足智能計算需求的今天,探索新一代軟硬件協(xié)同設計成為關鍵課題。

一、從圖靈完備到類腦計算完備的范式轉變

傳統(tǒng)圖靈完備性關注計算能力的理論邊界,而類腦計算完備性則強調對腦神經(jīng)信息處理機制的本質模擬。這種轉變要求計算系統(tǒng)不僅要實現(xiàn)符號邏輯處理,更要具備感知、學習、決策等類腦智能特征。張悠慧教授團隊指出,類腦計算完備的系統(tǒng)應當能夠有效處理不確定性、實現(xiàn)能效優(yōu)化,并具備自適應進化能力。

二、類腦計算硬件架構設計新思路

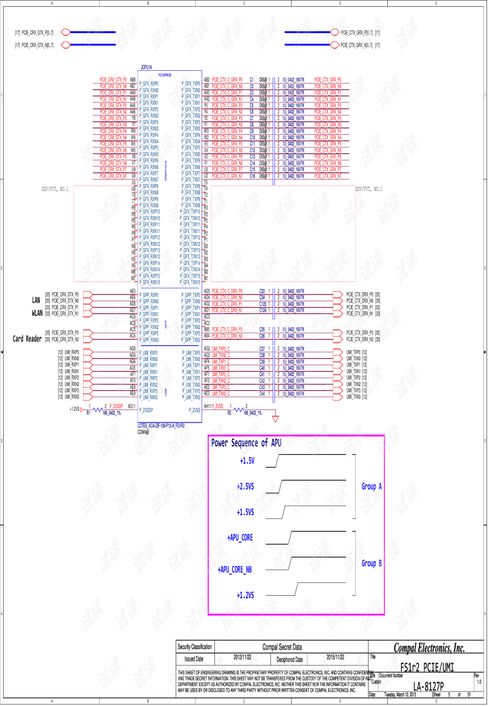

在硬件層面,需要突破傳統(tǒng)馮·諾依曼架構的瓶頸。具體設計方向包括:

- 存算一體架構:借鑒大腦神經(jīng)元與突觸的高度融合特性,開發(fā)新型憶阻器、相變存儲器等器件,實現(xiàn)存儲與計算的物理統(tǒng)一

- 異步事件驅動架構:摒棄傳統(tǒng)時鐘同步模式,采用脈沖神經(jīng)網(wǎng)絡(SNN)的異步事件處理機制

- 多尺度異構集成:在芯片層面實現(xiàn)數(shù)字、模擬、光電等多模態(tài)計算的協(xié)同

- 可重構計算陣列:根據(jù)任務需求動態(tài)配置計算資源,實現(xiàn)硬件資源的彈性分配

三、軟件棧與編程模型的創(chuàng)新設計

軟件層面需要建立全新的編程范式和工具鏈:

- 腦啟發(fā)編程語言:開發(fā)支持脈沖神經(jīng)網(wǎng)絡、Hebbian學習等腦機制的高級語言

- 跨層次編譯優(yōu)化:建立從算法到芯片的端到端編譯框架,實現(xiàn)算法與硬件的協(xié)同優(yōu)化

- 自適應運行時系統(tǒng):設計能夠根據(jù)環(huán)境變化動態(tài)調整計算策略的智能調度器

- 異構資源管理:開發(fā)統(tǒng)一的資源抽象層,屏蔽底層硬件差異

四、軟硬件協(xié)同設計的關鍵挑戰(zhàn)

實現(xiàn)類腦計算完備性面臨多重挑戰(zhàn):

- 能效瓶頸:如何在保證性能的同時大幅降低功耗

- 可擴展性:如何構建從單個芯片到大規(guī)模集群的統(tǒng)一架構

- 編程友好性:如何在保持高性能的同時降低開發(fā)門檻

- 可靠性保障:如何在非確定性計算中保證系統(tǒng)穩(wěn)定性

五、未來發(fā)展路徑與展望

張悠慧教授團隊建議采取漸進式發(fā)展策略:首先在特定領域實現(xiàn)類腦計算突破,然后逐步擴展到通用計算場景。未來需要建立跨學科研發(fā)團隊,融合神經(jīng)科學、計算機科學、微電子等多領域知識,共同推動類腦計算完備系統(tǒng)的實現(xiàn)。

這一技術路線的成功,將不僅推動人工智能技術的質的飛躍,更可能重塑整個計算產業(yè)的發(fā)展格局,為人類創(chuàng)造真正智能的計算系統(tǒng)開辟全新道路。